Block Interleaver Design for High Data Rate Wireless Networks

With increasing data rates in wireless

communication, quality of service (QoS) has become a

major issue. This is more with fading channels

transmitting huge volumes of data. QoS is degraded

by intersymbol interference (ISI) and related errors.

One of the simplest and convenient techniques to

overcome such errors is interleaving, which is used

efficiently in wireless applications. It has found

applications for combating burst errors that creeps

up in the channel during transmission. In this paper,

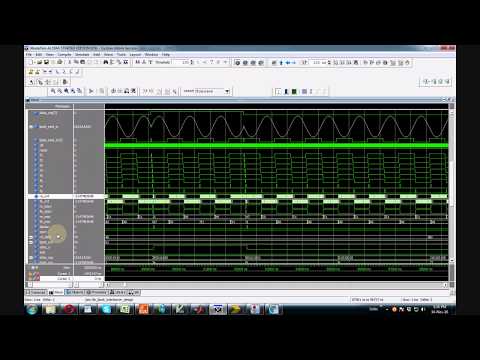

an efficient model of a block interleaver using a

hardware description language (Verilog) is proposed.

The proposed technique reduces consumption of

FPGA resources to a large extent, which implies low

power consumption. .

Comments are closed.